# Challenges for processor instruction extension in MPSoC Era

#### 1)Yoshinori Takeuchi and 2)Ryo Taketani

- 1) Dept. of Elect. & Elec. Eng., Kindai University

- 2) Grad. School of IST, Osaka University

- E-mail: takeuchi@ele.kindai.ac.jp

#### Introduction

#### □ IoT devices are of large variety

- Almost devices include at least one processor

- Application specific processings are required for IoT devices

- Configurable processors are expected to be a solution

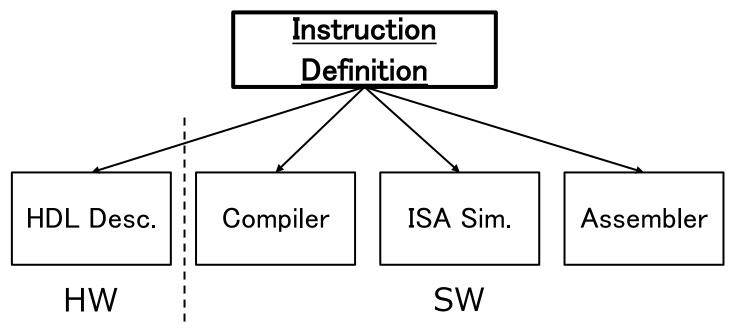

#### Problem for Instruction extensions

Hardware and software require separate descriptions for inst. extensions

⇒ Description amount is not small, and requires professional skills

University

#### Our challenge

- □ Simple and error free instruction extensions

- From unique instruction definition, <u>HW&SW</u> environments are generated

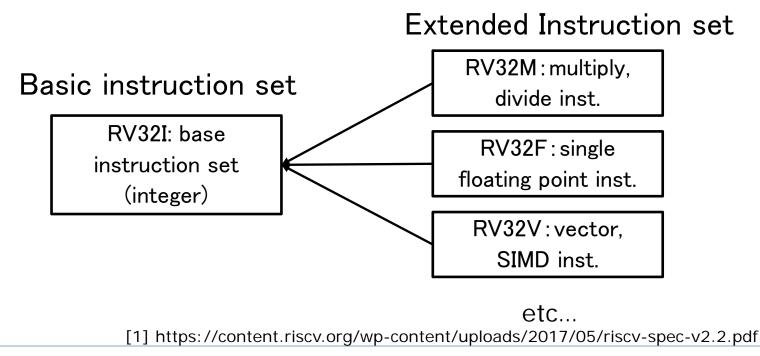

### RISC-V Instruction set [1]

- Open Instruction set Architecture

- □ ISA organization(32bit addressing mode)

(C) 2019 Yoshinori Takeuchi

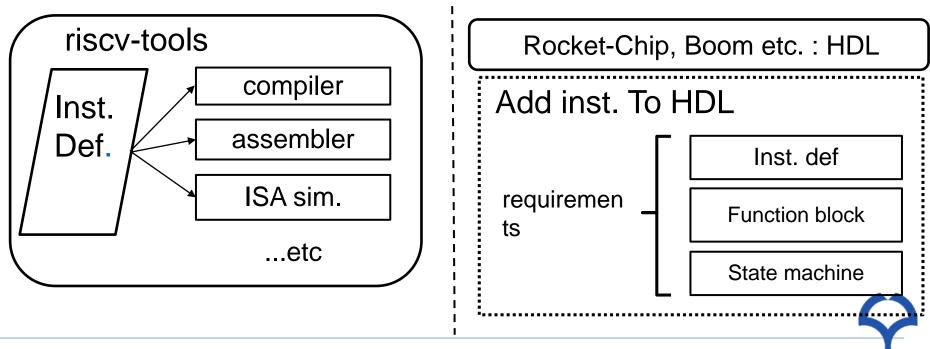

#### **RISC-V** Development Environment

- □ Fields for custom instructions

- Instruction Extension for SW & HW Dev. Env. SWs Dev. Env.

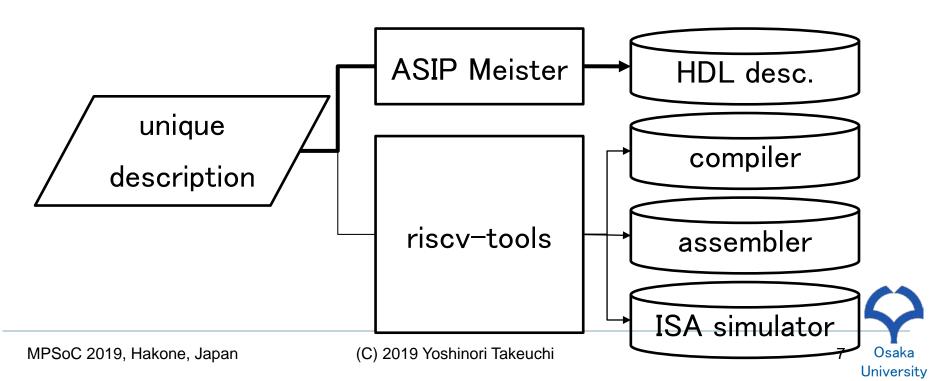

#### Basic idea and overview

From unique instruction definition, generate HW&SW environments for RISC-V processor with extended Instructions

#### Instruction extension on ASIP Meister 1

- ASIP Meister: Application domain-specific processor development environment

- 1. Opcode and operand definition

|            | Format                                | ABSO rd, rs1, rs2 |     |            |            |                |

|------------|---------------------------------------|-------------------|-----|------------|------------|----------------|

| Inst. type |                                       | MSB               | LSB | Field Type | Field Attr | Value          |

| <u>R</u>   |                                       | 31                | 25  | opcode     | binary     | 000000         |

| 1          |                                       | 24                | 20  | operand    | name       | rs2            |

| S          | ***<br>***                            | 19                | 15  | operand    | name       | rs1            |

| U          | ***                                   | 14                | 12  | opcode     | binary     | <u>000</u>     |

| В          | · · · · · · · · · · · · · · · · · · · | 11                | 7   | operand    | name       | rd             |

| J          | *****<br>***                          | 6                 | 0   | opcode     | binary     | <u>1010111</u> |

MPSoC 2019, Hakone, Japan

8 Osaka University

#### Instruction extension on ASIP Meister 2

2. Micro op. descriptions on each pipeline stage

| Stage                                                                  | Micro op. Description                                                                                                                                                                                                                        |  |  |  |  |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| VARIABLE                                                               | wire [31:0] source0;                                                                                                                                                                                                                         |  |  |  |  |

|                                                                        | wire [31:0] source1;<br>wire [31:0] result;                                                                                                                                                                                                  |  |  |  |  |

| IF                                                                     | FETCH()                                                                                                                                                                                                                                      |  |  |  |  |

| ID                                                                     | <pre>wire[31:0] temp0;<br/>wire[31:0] temp1;<br/>temp0 = GPR.read0(rs1);</pre>                                                                                                                                                               |  |  |  |  |

|                                                                        | <pre>temp1 = GPR.read1(rs2);<br/>source0 = FWU1.forward(rs1,temp0);<br/>source1 = FWU2.forward(rs2,temp1);</pre>                                                                                                                             |  |  |  |  |

| EXE                                                                    | <pre>wire [3:0] flag;<br/>wire [31:0] temp2;<br/>wire[31:0] reverse;<br/><temp2, flag=""> = ALU.sub(source0, source1);<br/>reverse = ~temp2;<br/>result = (temp2[31]) ? temp2 : reverse;<br/>null = FWU1.forward1(rd.result);</temp2,></pre> |  |  |  |  |

| MEM                                                                    | <pre>null = FWU2.forward1(rd,result);</pre>                                                                                                                                                                                                  |  |  |  |  |

| WB                                                                     | <pre>null = GPR.write0(rd, result);<br/>null = FWU1.forward3(rd.result);</pre>                                                                                                                                                               |  |  |  |  |

| null = FWU2.forward3(rd,result);<br>(C) 2019 Yoshinori Takeuchi 9 Osak |                                                                                                                                                                                                                                              |  |  |  |  |

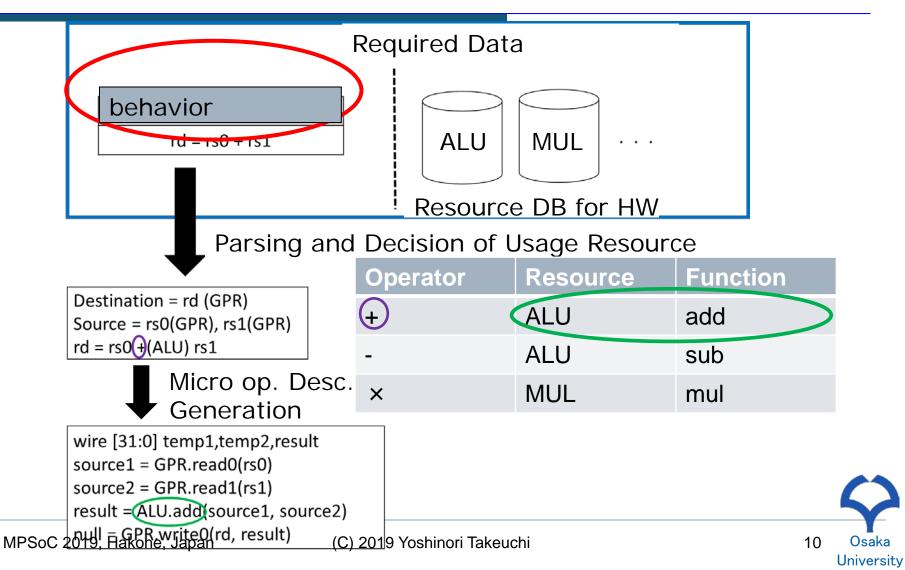

#### Micro op. description from Behavior

#### Conclusion and Future Work

- We introduce our challenges for processor instruction extension for RISC-V ISA based configurable processors

- □ Future work

- Trials for several ISA extension designs

- Evaluation by real examples

- Evaluation from several metrics of designed processors

#### Acknowledgment

## □ This work was partly supported by JSPS KAKENHI Grant Number JP17K00077.

### Thank you for your attention!

MPSoC 2019, Hakone, Japan

(C) 2019 Yoshinori Takeuchi